MSP430G2553 - MSP-FET

概要

MSP-FETは、Texas Instruments社が提供するMSP430マイコン用のプログラミングおよびデバッグツールである。

このツールは、JTAGインターフェース または Spy-Bi-Wire (SBW) インターフェースを使用して、MSP430マイコンとの通信を行う。

JTAG (Joint Test Action Group) は、元々はプリント基板のテストのために開発された標準規格である。

現在では、マイコンのプログラミングやデバッグに広く使用されている業界標準のインターフェースとなっている。

MSP-FETの主な機能には、以下に示すものがある。

- プログラムのダウンロード (フラッシュROMへの書き込み)

- リアルタイムデバッグ

- ブレークポイントの設定

- ステップ実行

- レジスタとメモリの監視

- Code Composer Studio (CCS) 等の統合開発環境との連携

MSP-FETは、USB経由でホストコンピュータに接続され、ターゲットのMSP430マイコンへは標準的な14ピンJTAGコネクタ または SBE (Spy-Bi-Wire) コネクタを使用して接続される。

このツールを使用することにより、開発者は効率的にプログラムの開発とデバッグを行うことができ、製品開発のサイクルを大幅に短縮することが可能となる。

MSP-FET、MSP-GANG430、MSP-PRGS430等のプログラマは、いずれも同じ接続方式をサポートしており、プロトタイプ基板から量産基板まで一貫した開発環境を提供する。

詳細な技術情報を知りたい場合は、MSP Debuggers User's Guide および MSP430 Flash Device Bootloader (BSL) User's Guide を参照すること。

また、MSP430G2553マイコンの情報を知りたい場合は、MSP430G2x13, MSP430G2x53 Mixed Signal Microcontroller データシート (SLAS735) を参照すること。

JTAG と Spy-Bi-Wireの違い

MSP-FETは、2つの異なる通信方式をサポートしている。

それぞれの方式には特徴があり、用途に応じて使い分けることができる。

JTAG方式 (4線式)

JTAGは、4本の信号線を使用する標準的なインターフェースである。

必要な信号線は以下の通りである。

- TDI (Test Data In)

- テストデータの入力信号

- TDO (Test Data Out)

- テストデータの出力信号

- TMS (Test Mode Select)

- テストモードの選択信号

- TCK (Test Clock)

- テストクロック信号

さらに、電源とグラウンドを含めると、標準的な14ピンJTAGコネクタでは以下に示す信号が使用される。

- VCC (Target voltage)

- ターゲットマイコンの電源電圧 (1.8[V]~3.6[V])

- GND (Ground)

- グラウンド

- RST (Reset)

- リセット信号

- TEST

- テスト信号

JTAG方式は、ほぼ全てのMSP430デバイスでサポートされており、高速なデータ転送と安定した動作が特徴である。

ただし、ピン数の少ないデバイス(例:MSP430G2230)では、JTAG方式がサポートされていない場合がある。

開発の初期段階やプロトタイプの作成時には、JTAG方式を使用することが推奨される。

SBW (Spy-Bi-Wire) 方式 (2線式)

SBW (Spy-Bi-Wire) は、2本の信号線のみを使用する省ピンインターフェースである。

これは、Texas Instruments社が開発したMSP430専用のインターフェースである。

必要な信号線は以下の通りである。

- SBWTDIO (Spy-Bi-Wire Test Data Input/Output)

- データ入出力の双方向信号 (RST/NMIピンと共用)

- SBWTCK (Spy-Bi-Wire Test Clock)

- クロック信号(TESTピンと共用)

SBW (Spy-Bi-Wire) 方式のメリットは、使用するピン数が少ないため、製品の最終基板設計において貴重なピンを節約できることである。

また、4ピンコネクタ (SBWTDIO、SBWTCK、VCC、GND) で接続できるため、プリント基板上のスペースも節約できる。

ただし、SBW (Spy-Bi-Wire)方式は、JTAG方式と比較してデータ転送速度がやや遅い場合がある。

また、全てのMSP430デバイスがSBW (Spy-Bi-Wire)をサポートしているわけではないため、使用する各MSP430ファミリーのデータシートで対応状況を確認する必要がある。

一般的に、MSP430F2xx、MSP430G2xx、F4xx、F5xx、F6xx、FRxxファミリーの多くのマイコンがSBW (Spy-Bi-Wire) をサポートしている。

MSP430G2553は、JTAGとSBW (Spy-Bi-Wire) の両方をサポートする最新世代のデバイスである。

MSP430マイコンのピン対応

SBW (Spy-Bi-Wire) が推奨される理由として、MSP430G2553のような小型のマイコンでは、JTAGピンがI/Oポートと共有されている。

SBW (Spy-Bi-Wire) を使用すれば、RSTとTESTの2本だけでデバッグできるため、他のピンをGPIOやSPI等の通信に使用できる。

(JTAGではピンの競合が発生する可能性がある)

| 項目 | MSP430F149 | MSP430F2013 | MSP430F5529 | MSP430G2553 |

|---|---|---|---|---|

| 基本仕様 | ||||

| パッケージ | 64ピンLQFP | 14ピンTSSOP/PDIP | 64ピンRGC (VQFN) 80ピンPN (LQFP) |

20ピンPDIP/TSSOP/VQFN 28ピンTSSOP 32ピンQFN |

| デバイス特性 | 大型デバイス | 小型デバイス | USB対応マイコン | 汎用小型デバイス |

| ピン設計 | ポートピン (P4.4~P4.7) との多重化 | 省ピン設計により、多くのピンをアプリケーションに使用可能 | ポートピン (PJ.0~PJ.3) との多重化 USB機能搭載 |

ポートピン (P1.4~P1.7) との多重化により柔軟な設計が可能 |

| 用途の特徴 | 古い世代のデバイスで、専用JTAGピンを持つ設計 | 限られたピン数で最大限の機能を実現 | USB接続が必要なアプリケーション データロガー、センサシステム |

開発時と製品化時で異なるインターフェースを選択可能 省電力アプリケーションに最適 |

| デバッグインターフェース対応 | ||||

| 4線式JTAG | サポート | サポート | サポート | サポート |

| 2線式Spy-Bi-Wire | - | サポート | サポート | サポート |

| 電源ピン | ||||

| VCC/AVCC/DVCC | ピン48 (DVCC) ピン60 (AVCC) |

ピン1 (VCC) | 64ピンRGC: ピン33 (DVCC2) ピン15 (DVCC1) ピン11 (AVCC1) 80ピンPN: ピン50 (DVCC2) ピン18 (DVCC1) ピン11 (AVCC1) |

20ピンPDIP/TSSOP/VQFN: ピン1 (DVCC) 28ピンTSSOP: ピン1 (DVCC) 32ピンQFN: ピン30 (DVCC) |

| VSS/AVSS/DVSS | ピン49 (DVSS) ピン61 (AVSS) |

ピン14 (VSS) | 64ピンRGC: ピン34 (DVSS2) ピン16 (DVSS1) ピン14 (AVSS1) 80ピンPN: ピン49 (DVSS2) ピン19 (DVSS1) ピン14 (AVSS1) |

20ピンPDIP/TSSOP/VQFN: ピン20 (DVSS) 28ピンTSSOP: ピン28 (DVSS) 32ピンQFN: ピン27, 28 (DVSS) |

| Spy-Bi-Wire信号線 | ||||

| RST/NMI/SBWTDIO | - | ピン10 (RST/NMI/SBWTDIO) | 64ピンRGC: ピン64 (RST/NMI/SBWTDIO) 80ピンPN: ピン76 (RST/NMI/SBWTDIO) |

20ピンPDIP/TSSOP/VQFN: ピン16 (RST/NMI/SBWTDIO) 28ピンTSSOP: ピン24 (RST/NMI/SBWTDIO) 32ピンQFN: ピン23 (RST/NMI/SBWTDIO) |

| TEST/SBWTCK | - | ピン11 (TEST/SBWTCK) | 64ピンRGC: ピン59 (TEST/SBWTCK) 80ピンPN: ピン71 (TEST/SBWTCK) |

20ピンPDIP/TSSOP/VQFN: ピン17 (TEST/SBWTCK) 28ピンTSSOP: ピン25 (TEST/SBWTCK) 32ピンQFN: ピン24 (TEST/SBWTCK) |

| 4線式JTAG信号線 | ||||

| TCK | ピン5 (P4.4/TCK) | ピン6 (P1.4/SMCLK/A2+/TCK) | 64ピンRGC: ピン63 (PJ.3/TCK) 80ピンPN: ピン75 (PJ.3/TCK) |

20ピンPDIP/TSSOP/VQFN: ピン6 (P1.4/SMCLK/TCK) 28ピンTSSOP: ピン6 (P1.4/SMCLK/TCK) 32ピンQFN: ピン4 (P1.4/SMCLK/TCK) |

| TMS | ピン3 (P4.5/TMS) | ピン7 (P1.5/TA0/A2-/SCLK/TMS) | 64ピンRGC: ピン62 (PJ.2/TMS) 80ピンPN: ピン74 (PJ.2/TMS) |

20ピンPDIP/TSSOP/VQFN: ピン7 (P1.5/TA0.0/TMS) 28ピンTSSOP: ピン7 (P1.5/TA0.0/TMS) 32ピンQFN: ピン5 (P1.5/TA0.0/TMS) |

| TDI/TCLK | ピン4 (P4.6/TDI) | ピン8 (P1.6/TA1/A3+/SDO/SCL/TDI/TCLK) | 64ピンRGC: ピン61 (PJ.1/TDI/TCLK) 80ピンPN: ピン73 (PJ.1/TDI/TCLK) |

20ピンPDIP/TSSOP/VQFN: ピン14 (P1.6/TA0.1/TDI/TCLK) 28ピンTSSOP: ピン14 (P1.6/TA0.1/TDI/TCLK) 32ピンQFN: ピン21 (P1.6/TA0.1/TDI/TCLK) |

| TDO/TDI | ピン1 (P4.7/TDO) | ピン9 (P1.7/A3-/SDI/SDA/TDO/TDI) | 64ピンRGC: ピン60 (PJ.0/TDO) 80ピンPN: ピン72 (PJ.0/TDO) |

20ピンPDIP/TSSOP/VQFN: ピン15 (P1.7/CAOUT/TDO/TDI) 28ピンTSSOP: ピン23 (P1.7/CAOUT/TDO/TDI) 32ピンQFN: ピン22 (P1.7/CAOUT/TDO/TDI) |

| 追加仕様 | ||||

| クロック速度 | 最大8[MHz] | 最大16[MHz] | 最大25[MHz] (PMMCOREVx設定による) |

VCC=1.8Vで最大6[MHz] VCC=2.7Vで最大12[MHz] VCC=3.6Vで最大16[MHz] |

| フラッシュROM / RAM容量 | 60[KB] / 2[KB] | 2[KB] / 128[B] | 128[KB] / 8[KB] | 16[KB] / 512[B] |

| 特記事項 | 4線式JTAG専用 TESTピンは専用ピンとして存在しない |

2線式Spy-Bi-Wire専用 4線式JTAGピンは存在しない |

USB 2.0対応 12ビットADC搭載 両方のJTAGモードをサポート |

両方のJTAGモードをサポート JTAGピンはGPIOと共用可能 10ビットADC搭載 LaunchPad開発キット対応 |

接続方法

電源供給方法の選択

MSP-FETおよびMSP-GANG430は、ターゲット基板への電源供給機能を持っている。

電源供給方法には、以下の2つの選択肢がある。

ツールから電源を供給する場合(VCC_TOOL使用)

- 14ピンJTAGコネクタのピン2 (VCC_TOOL) に接続する。

- ターゲット基板に独自の電源がない場合に使用する。

- ピン4 (VCC_TARGET) には接続しない。

ターゲット基板の独自電源を使用する場合(VCC_TARGET使用)

- 14ピンJTAGコネクタのピン4(VCC_TARGET)に接続する

- ターゲット基板がバッテリーや独自電源を持つ場合に使用

- VCC_SENSE機能により、MSP-FETが基板の電源電圧を検出し、それに応じて出力信号を調整する

- 電源競合を防ぐため、ピン2(VCC_TOOL)には接続しない

※注意

ピン2とピン4を同時に接続してはならない。

電源競合により、MSP-FETまたはターゲット基板を破損する可能性がある。

両方の電源供給方法に対応するため、ジャンパブロックを使用して切り替え可能な設計にすることができる。

柔軟性が不要な場合は、必要な接続方法を直接配線してジャンパブロックを省略することもできる。

14ピンJTAG接続

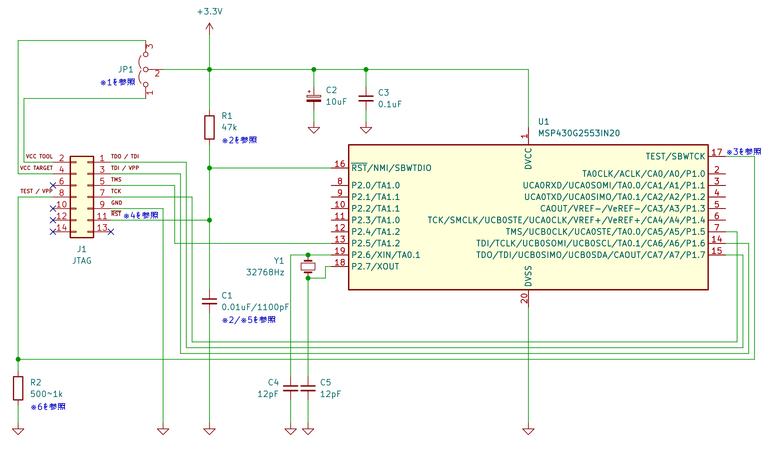

下図に、MSP430G2553マイコンと14ピンJTAGコネクタとの接続を示す。

- ※注記1 - 電源供給の選択

- ターゲットボード側でローカル電源を使用する場合は JP1 - 3 を接続する。

- MSP-FETから電源を供給する場合は JP1 - 1 を接続する。

- ※注記2 - RST/NMIピンのR1とC1の設定

- RST/NMIピンのR1とC1の構成はデバイスファミリーにより異なる。

- MSP430G2553では、回路図に示されているように 47[kΩ]のプルアップ抵抗 と 1.1[nF] (または 100[pF]~2.2[nF]の範囲) のコンデンサ が標準的な値である。

- これにより、リセット信号のノイズ耐性と適切な立ち上がり時間を確保する。

- MSP430G2553は両方のJTAGモードに対応しているため、4線式JTAGを使用する場合でもC1の上限は2.2[nF]を超えてはならない。

- MSP430G2553のデータシートの「JTAG and Spy-Bi-Wire Interface」セクションでも、このRSTピン回路の推奨値が記載されている。

- ※注記3 - TESTピンの有無

- TESTピンは、多重化されたJTAGピンを持つMSP430ファミリーメンバーで使用可能である。

- MSP430G2553にはTEST/SBWTCKピン (20ピンパッケージではピン17) が存在する。

- このピンは、Spy-Bi-Wire通信ではSBWTCKクロック信号として使用され、4線式JTAG通信でもテストモード選択に使用される。

- 内部プルダウン抵抗 (25[kΩ]~90[kΩ]、典型値60[kΩ]) が実装されているが、基板設計では追加の外部プルダウン抵抗は通常不要である。

- ※注記4 - JTAGコネクタRSTピン接続の必要性

- JTAGコネクタのRSTピンへの接続は、SBW (Spy-Bi-Wire) 通信をサポートするデバイスをプログラミングまたはデバッグする場合に必須である。

- これは、4線式JTAG通信を使用している場合でも同様である。

- MSP430G2553は両方のJTAG通信モードに対応しているため、JTAGコネクタのRSTピン接続は必須である。

- この接続により、以下の機能が確保される:

- JTAGコマンドによるリセットが失敗した場合の予備手段として機能する。

- デバッグツールが確実にデバイスをリセットすることができる。

- Spy-Bi-Wire通信モードではRST/NMI/SBWTDIOピンとして双方向データ通信に使用される。

- ※注記5 - SBW (Spy-Bi-Wire) 通信デバイスでのC1容量制限

- SBW (Spy-Bi-Wire) 通信をサポートするMSP430G2553をJTAG通信で使用する場合でも、C1の上限値は2.2[nF]を超えてはならない。

- SBW (Spy-Bi-Wire) 通信の典型値は1.1[nF]である。

- この範囲は、SBW速度、電圧、基板設計により、100[pF]~2.2[nF]の間で変化することがある。

- MSP430G2553では、RST/NMI/SBWTDIOピンのC1として 1.1[nF]が推奨値 である。

- この値により、リセット信号のノイズフィルタリングと適切なデバウンス特性が得ることができる。

- この容量制限は、4線式JTAG使用時にも適用される重要な設計ガイドラインである。

- ※注記6 - ノイズ・ESD対策のプルダウン抵抗

- 過度なノイズやESD (静電気放電) が懸念される用途では、ターゲットデバイスの適切なプログラミングを維持しながら、

- 500[Ω]~1[kΩ]のプルダウン抵抗をTEST/SBWTCKピンに追加することができる。

- MSP430G2553にはTEST/SBWTCKピン (20ピンパッケージではピン17) が存在する。

- 内部プルダウン抵抗 (典型値60[kΩ]) が実装されているが、高ノイズ環境では以下に示す事柄に注意すること。

- JTAGピン (TDO/TDI、TDI/TCLK、TMS、TCK) およびTEST/SBWTCKピンにはESD保護回路が内蔵されているが、高ノイズ環境では信号ラインに直列抵抗 (22[Ω]~47[Ω]程度) または追加のプルダウン抵抗 (500[Ω]~1[kΩ]) の追加を検討する。

- GNDプレーンを適切に配置して、信号ラインの長さを最小限に抑える。

- TEST/SBWTCKピンへの追加プルダウン抵抗は、Spy-Bi-Wire通信使用時に特に有効である。

※注意

JTAG通信の接続時において、以下に示す事柄を確認する必要がある。

- ピン1の位置を正しく確認すること。

コネクタには通常、切り欠きやマークでピン1が示されている。 - ターゲット基板の電源電圧が、MSP-FETの対応範囲 (1.8[V]~3.6[V]) 内であることを確認すること。

ただし、フラッシュROMのプログラミングまたは消去時は2.2[V]~3.6[V]の範囲が必要である。 - MSP-FETはターゲット基板の電源電圧を検出して動作するため、ターゲット基板に電源が供給されていることを確認すること。

SBW (Spy-Bi-Wire) 接続

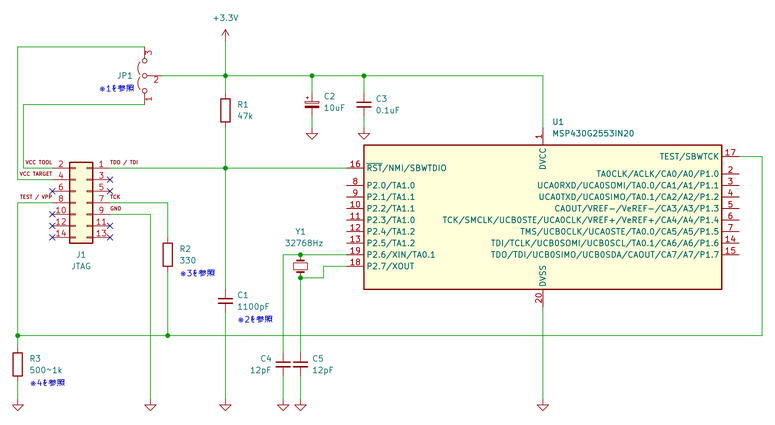

下図に、MSP430G2553マイコンとSBW (Spy-Bi-Wire) コネクタとの接続を示す。

MSP430G2553は、SBW (Spy-Bi-Wire) 通信に完全対応している。

- ※注記A - 電源供給の選択

- ターゲットボード側でローカル電源を使用する場合は JP1 - 3 を接続する。

- MSP-FETから電源を供給する場合は JP1 - 1 を接続する。

- ※注記B - RST/NMI/SBWTDIOピンの容量制限

- RST/NMI/SBWTDIOピンは、Spy-Bi-Wire通信モードでJTAGアクセス中に双方向通信に使用される。

- このピンに接続されている容量は、デバイスとの接続確立能力に影響を与える可能性がある。

- そのため、以下に示す事柄を遵守する必要がある:

- C1の上限値: 2.2[nF] (2200[pF])

- Spy-Bi-Wire通信の標準値: 1.1[nF] (1100[pF])

- C1の範囲: 100[pF]~2.2[nF] (2200[pF])

- SBW速度、電圧、基板設計により範囲内で調整が必要である。

- MSP430G2553固有の推奨値については、データシートを参照すること。

- ※注記C - TEST/SBWTCKピンの保護抵抗

- MSP430F2xx、MSP430G2xx、MSP430F4xxファミリーでは、R2 (330[Ω]の保護抵抗) が必要である。

- R2は、ヒューズブロープロセス中にTEST/VPPピンから供給されるJTAGセキュリティヒューズブロー電圧から、JTAGデバッグインターフェースのTCK信号を保護する。

- ヒューズブロー機能が不要な場合、R2は不要である (0[Ω]を実装) 。

- また、ヒューズブロー機能を使用しない場合は、TEST/VPPをTEST/SBWTCKに接続しないこと。

- MSP430G2553では、ヒューズブロー機能を使用する場合、以下の条件が必要である:

- 供給電圧VCC: 2.5[V] (25℃時)

- TESTピンのヒューズブロー電圧VFB: 6[V]~7[V]

- ヒューズブロー中のTESTピンへの供給電流IFB: 最大100[mA]

- ヒューズブロー時間tFB: 最大1[ms]

- ヒューズが一度ブローされると、JTAG/Test、Spy-Bi-Wire、エミュレーション機能へのアクセスは不可能となり、JTAGはバイパスモードに切り替わる。

- ※注記D - ノイズ・ESD対策のプルダウン抵抗

- 過度なノイズやESD (静電気放電) が懸念される用途では、ターゲットデバイスの適切なプログラミングを維持しながら、

- 500[Ω]~1[kΩ]のプルダウン抵抗をTEST/SBWTCKピンに追加することができる。

- MSP430G2553には内部プルダウン抵抗 (25[kΩ]~90[kΩ]、典型値60[kΩ]) が実装されているが、

- 高ノイズ環境では追加の外部プルダウン抵抗の追加を検討すること。

※注意1

一部のSpy-Bi-Wire対応のMSP430デバイスでは、TEST/SBWTCKピンが立ち上がり信号エッジに非常に敏感である。

意図しないエッジ信号により、テストロジックが正常にエントリシーケンスを認識できない状態に入り、JTAGアクセスが無効化される可能性がある。

JTAGコネクタをターゲットデバイスに接続する時に、このような意図しないエッジが発生することがある。

MSP430G2553も同様の特性を持つため、接続時には注意が必要である。

※注意2

- 接続前に、必ずターゲット基板の電源電圧を確認すること。電圧が範囲外の場合、MSP-FETやターゲットマイコンを破損する可能性がある。

- 接続は、ターゲット基板の電源をOFFにした状態で行うことが推奨される。

- MSP-FETとターゲット基板のグラウンドが確実に接続されていることを確認すること。

グラウンドの接続が不十分な場合、通信エラーや動作不良の原因となる。 - ケーブルの長さは、できるだけ短くすること。

長いケーブルは、ノイズの影響を受けやすく通信エラーの原因となる。

一般的に、0.2[m]以下が推奨される。 - ピン2 (VCC_TOOL) と ピン4 (VCC_TARGET) を同時に接続してはならない。

RST/NMIピンのコンデンサC1容量の選定ガイド

RST/NMIピンに接続するコンデンサC1の上限値は、SBW (Spy-Bi-Wire) 機能の有無によって異なる。

コンデンサC1の上限値一覧

| マイコンの種類 | デバッグ インターフェース |

C1の容量 | 備考 |

|---|---|---|---|

| SBW対応 MSP430マイコン (MSP430G2553等) |

JTAG | 2200[pF]以下 (推奨 : 100[pF]~2200[pF] 典型値 : 1100[pF]) |

JTAGを使用する場合でも上限は2200[pF] SBWと同じ制限が適用される |

| SBW | 2200[pF]以下 (推奨 : 100[pF]~2200[pF] 典型値 : 1100[pF]) |

典型値は、1100[pF]程度 | |

| SBW非対応 旧世代MSP430 (MSP430F149等) |

JTAG | 0.01[µF] 程度 (10000[pF]) |

RST/NMIがリセット専用のため容量制限なし |

容量制限の理由

SBW対応マイコン(MSP430G2553等)では、RST/NMI/SBWTDIOピンがリセット信号と双方向データ通信の2つの機能を持つ。

このため、4線式JTAGインターフェース使用時でもSBWと同じ容量制限が適用される。

大容量コンデンサは充放電に時間を要し、信号の立ち上がり/立ち下がり時間が長くなることでSBW通信エラーやデバイス認識の失敗を引き起こす。

2200[pF]という上限値は、MSP-FETファームウェアとCode Composer Studioでの安定動作が保証されている値である。

最適値は下表の条件により変動するため、100[pF]~2200[pF]の範囲内で調整が推奨される。

| 要因 | 影響内容 |

|---|---|

| SBW通信速度設定 | 通信速度が高いほど小さい容量が必要。 MSP430G2553のSBW入力周波数は最大20[MHz]である。 |

| ターゲット基板の電源電圧 | 電圧が低いと信号の立ち上がり時間が長くなる。 MSP430G2553の動作電圧範囲は1.8[V]~3.6[V]である。 |

| 基板レイアウト | 配線長が長い または 寄生容量が大きいと信号品質が低下する。 |

| ノイズ環境 | ノイズが多い環境では安定性のため調整が必要。 |

基板設計時の重要事項

- 使用するMSP430マイコンのデータシートでSBW機能の有無を確認する。(MSP430G2553はSBW対応)

- 典型値として1100[pF]程度を使用する。

- 通信が不安定な場合は、100[pF]~2200[pF]の範囲で調整する。

- ノイズ対策が必要な場合はTEST/SBWTCKピンに500[Ω]~1[kΩ]のプルダウン抵抗を追加可能。

- MSP430G2553には内部プルダウン抵抗 (典型値60[kΩ]) が実装されているため、通常は外部プルダウン抵抗は不要である。

※注意

この容量制限は安定したデバッグ接続を確保するための重要な設計ガイドラインであるため、基板設計時には必ず遵守すること。

特にMSP430G2553のような両方のJTAGモードに対応したデバイスでは、4線式JTAG使用時にもこの制限が適用される点に注意すること。

トラブルシューティング

MSP-FETがデバイスを認識できない場合、以下に示す事柄を確認する。

- C1の容量が2200[pF]以下であること。

- 配線長を可能な限り短くし、寄生容量を最小化する。

- SBW通信速度の設定を下げて試す。(MSP430G2553のSBW入力周波数仕様: 0~20[MHz])

- C1の容量を段階的に小さくする。(例 : 1100[pF] -> 470[pF] -> 100[pF])

- ノイズやESDの影響が懸念される場合は、TEST/SBWTCKピンに500[Ω]~1[kΩ]のプルダウン抵抗を追加する。

- 電源電圧を確認する。(通常動作: 1.8[V]~3.6[V]、フラッシュプログラミング: 2.2[V]~3.6[V])

ターゲット基板の設計上の考慮事項

MSP-FETを使用してデバッグを行うためには、ターゲット基板の設計時に重要な事柄を考慮する必要がある。

これらの考慮事項を無視する場合、デバッグが困難あるいは不可能になる場合がある。

JTAGピンの保護

JTAGピン (TDI/TCLK、TDO/TDI、TMS、TCK) は、製品の最終動作時には通常使用されないが、開発やデバッグ時には重要である。

MSP430G2553では、これらのJTAGピンはP1.4~P1.7ポートピンと多重化されている。

つまり、これらのピンは、他の回路要素から適切に保護される必要がある。

特に注意すべき事柄として、JTAGピンには直列抵抗を接続しないことが挙げられる。

直列抵抗は、信号の立ち上がりと立ち下がりを遅くし、通信エラーの原因となる可能性がある。

もし、JTAGピンを他の目的でも使用する必要がある場合は、0[Ω]抵抗や小さな値の抵抗 (22[Ω]~47[Ω]) を使用して、製品化時にはこれらをショートすることを検討する。

MSP430G2553の20ピンパッケージでは、以下のピンがJTAGとGPIOで多重化されている:

- ピン6 (P1.4/SMCLK/TCK) - JTAG: TCK、GPIO: P1.4、または SMCLK出力

- ピン7 (P1.5/TA0.0/TMS) - JTAG: TMS、GPIO: P1.5、または Timer_A0 出力

- ピン14 (P1.6/TA0.1/TDI/TCLK) - JTAG: TDI/TCLK、GPIO: P1.6、または Timer_A0 出力

- ピン15 (P1.7/CAOUT/TDO/TDI) - JTAG: TDO/TDI、GPIO: P1.7、または Comparator_A+ 出力

製品の最終段階では、これらのピンをGPIOやその他の機能に使用できるが、開発段階ではJTAG機能として確保しておくことが推奨される。

デカップリングコンデンサ

MSP430G2553マイコンの電源ピンには、必ずデカップリングコンデンサ (0.1[µF]のセラミックコンデンサ C3) を、DVCCピンとDVSSピンの間にできるだけ近い位置に必ず配置する必要がある。

これは、マイコンの急激な電流変化を吸収して、電源電圧の安定化に寄与する役割がある。

また、デバッグ時の通信エラーを防ぐために重要である。

また、追加コンデンサ (10[µF]程度の容量の大きいコンデンサ C2) の配置も推奨される。

これは、電源ライン全体を安定化させるためである。

MSP430G2553の20ピンパッケージでは、ピン1がDVCC、ピン20がDVSSである。

デカップリングコンデンサは、これらのピンのできるだけ近くに配置すること。

RSTピン

RSTピン (リセットピン) は、JTAGインターフェースにおいて重要である。

このピンは、デバッグ開始時において、MSP430G2553マイコンをリセット状態 (初期化) にするために使用される。

MSP430G2553の20ピンパッケージでは、ピン16がRST/NMI/SBWTDIOである。

RSTピン回路

47[kΩ]のプルアップ抵抗をDVCCとRSTピンの間に接続する。

これは、RSTピンがフローティング状態になることを防ぎ、意図しないリセットを防止するためである。

リセットボタンを使用する場合

RSTピンの信号がLowになる時、RSTピンがGNDに接続されて、MSP430G2553マイコンがリセットされる。

また、チャタリングを防止するため、コンデンサC1をRSTピンとGNDの間に配置する。

MSP430G2553では、RST/NMI/SBWTDIOピンがSpy-Bi-Wire通信の双方向データ線としても機能するため、コンデンサC1の値には厳格な制限がある。

14ピンJTAG使用時

MSP430G2553は両方のJTAGモードに対応しているため、4線式JTAG通信を使用する場合でもC1の上限は2200[pF]を超えないようにする。

典型値として1100[pF]、範囲としては100[pF]~2200[pF]が推奨される。

SBW (Spy-Bi-Wire) 使用時

Spy-Bi-Wire通信を使用する時、RST/NMI/SBWTDIOピンがJTAGアクセス中に双方向通信に使用される。

このピンに接続されている容量は、デバイスとの接続確立能力に影響を与える可能性がある。

そのため、以下に示す事柄を遵守する必要がある。

- C1の上限値

- 2200[pF]

- Spy-Bi-Wire通信の標準値

- 1100[pF]

- C1の範囲

- 100[pF]~2200[pF]

- ただし、SBW速度、電圧、基板設計により変わる。

- MSP430G2553のSBW通信仕様:

- SBW入力周波数: 0~20[MHz] (VCC = 2.2V以上)

- SBWローパルス幅: 0.025~15[µs] (VCC = 2.2V以上)

- SBW有効化時間: 最大1[µs] (TEST信号High後、最初のクロックエッジ受付まで)

- SBW通常動作復帰時間: 15~100[µs] (VCC = 2.2V以上)

TESTピン

TESTピンは、MSP430マイコンをJTAGモードに入れるために使用される特別なピンである。

MSP430G2553の20ピンパッケージでは、ピン17がTEST/SBWTCKである。

接続

MSP430G2553には、TEST/SBWTCKピンに内部プルダウン抵抗 (25[kΩ]~90[kΩ]、典型値60[kΩ]) が実装されている。

そのため、通常の用途では外部プルダウン抵抗は不要である。

ただし、過度なノイズやESD (静電気放電) が懸念される用途では、500[Ω]~1[kΩ]の外部プルダウン抵抗を追加接続することが推奨される。

プルダウン抵抗は、TEST/SBWTCKピンを確実にLowレベルに保つために使用する。

TEST/SBWTCKピンの信号がHighになる時、MSP430G2553マイコンはJTAGモードに入り、通常の動作を停止する。

製品の出荷時においては、TEST/SBWTCKピンはLowレベルに保たれる必要がある。

※注意

Spy-Bi-Wire通信を使用する場合、TEST/SBWTCKピンはSBWTCK (クロック信号) として使用されるため、プルダウン抵抗の接続が特に重要となる。

ただし、MSP430G2553には内部プルダウン抵抗が実装されているため、一般的な用途では外部プルダウン抵抗は不要である。

ヒューズブロー機能使用時の注意

MSP430F2xx、MSP430G2xx、MSP430F4xxファミリーでは、セキュリティヒューズブロー機能をサポートしている。

この機能を使用する場合、TEST/VPPピンに高電圧 (6[V]~7[V]) を印加する必要がある。

ヒューズブロー機能を使用する場合は、Spy-Bi-Wire接続回路のR2 (330[Ω]の保護抵抗) が必要となる。

この抵抗は、JTAGデバッグインターフェースのTCK信号をヒューズブロー電圧から保護するためである。

ヒューズが一度ブローされると、JTAG/Test、Spy-Bi-Wire、エミュレーション機能へのアクセスは完全に不可能となり、JTAGはバイパスモードに切り替わる。

この操作は不可逆的であるため、製品の最終出荷時のみに実行すること。

基板設計

製品の最終基板では、必ずJTAGコネクタ または Spy-Bi-Wireコネクタを実装する。

これにより、製造後のトラブルシューティングが可能となる。

JTAGコネクタ または Spy-Bi-Wireコネクタのスペースが限られている場合は、テストポイント (パッド) を配置することを検討すること。

なお、テストポイントは、ポゴピンアダプタや治具を使用して接続することができる。

※注意

JTAGピン (P1.4~P1.7) をGPIOとして使用する場合は、プログラミング時にこれらのピンが正しく動作するように、適切な保護回路を実装すること。

RSTピンとTESTピンの抵抗とコンデンサの値は、MSP430ファミリーによって異なる場合があるため、必ずMSP430ファミリーのユーザーガイドとデバイス固有のデータシートを参照すること。

MSP430G2553では、RST/NMI/SBWTDIOピンのC1容量は2200[pF]以下 (典型値1100[pF]) である点に特に注意すること。

プログラミングとデバッグの手順

初回接続とデバイスの認識

MSP-FETを初めて使用する場合 または 新しいターゲット基板に接続する場合には、以下に示す手順を実行する。

- まず、MSP-FETをUSB経由でPCに接続する。

- ドライバが自動的にインストールされ、デバイスとして認識される。

Windows環境では、デバイスマネージャでMSP-FETが正しく認識されていることが確認できる。 - 次に、ターゲット基板に電源を供給する。

MSP-FETは、ターゲット基板から電源電圧を検出するため、ターゲット基板に電源が供給されていることが必須である。

MSP430G2553の動作電圧範囲は1.8[V]~3.6[V]である (ただし、フラッシュROMのプログラミングまたは消去時は2.2[V]~3.6[V])。 - MSP-FETとターゲット基板をJTAGケーブル または Spy-Bi-Wireケーブルで接続する。

MSP430G2553は両方のインターフェースに対応しているため、用途に応じて選択できる。 - Code Composer Studioを起動して、デバッグ設定を行う。

デバッグ設定では、使用するデバッガ (MSP-FET) と ターゲットデバイス (MSP430G2553) を選択する。

接続モード (4線式JTAG または 2線式Spy-Bi-Wire) も選択する。 - [接続]ボタンを押下すると、Code Composer StudioはMSP-FETを介してターゲットマイコンと通信を試みる。

- 接続が成功した場合、MSP430G2553マイコンのデバイス情報が表示されてデバッグが可能となる。

デバイス情報には、デバイスID、フラッシュROMサイズ (16[KB])、RAMサイズ (512[B]) などが含まれる。

※注意

MSP430G2553を初めて使用する場合、Code Composer Studioの最新版を使用することが推奨される。

古いバージョンのCode Composer StudioやMSP-FETファームウェアでは、MSP430G2553を正しく認識できない場合がある。

プログラムのダウンロード

プログラムをMSP430G2553にダウンロードする手順は、使用する開発環境によって若干異なるが、基本的な流れは同じである。

- まず、ソースコードをコンパイルして、実行可能ファイル (通常は.outまたは.elfファイル) を生成する。

この時、コンパイルエラーがある場合は、それらを修正してから次に進む。 - 次に、Code Composer Studioのダウンロード機能 または プログラム機能を使用して、実行可能ファイルをMSP430G2553のフラッシュROMに書き込む。

この処理には、通常数秒から数十秒掛かる。

MSP430G2553のフラッシュROMは16[KB]であり、512バイトのセグメントに分割されている。 - 書き込みが完了した時、Code Composer Studioは書き込まれたプログラムを検証して、正しく書き込まれたことを確認する。

- 検証が成功した時、プログラムはMSP430G2553マイコンに正常にダウンロードされたことになる。

- MSP430G2553をリセットすると、新しくダウンロードされたプログラムが実行される。

※注意

フラッシュROMへの書き込み時は、電源電圧が2.2[V]~3.6[V]の範囲内であることを確認すること。

電源電圧が2.2[V]未満の場合、フラッシュROMのプログラミングまたは消去は正常に動作しない。

デバッグの実行

デバッグは、プログラムの動作を確認して、バグを発見して修正するための重要なプロセスである。

MSP-FETは、強力なデバッグ機能を提供し、効率的なデバッグを可能にする。

ブレークポイントは、プログラムの実行を一時停止させるために使用される。

ソースコードの特定の行にブレークポイントを設定すると、プログラムがその行に到達したときに自動的に停止する。

MSP430G2553では、ハードウェアブレークポイントが2個まで使用できる (EEM - Enhanced Emulation Module の仕様による)。

ステップ実行は、プログラムを1行ずつ実行する機能である。

ステップイン、ステップオーバー、ステップアウトなどの機能を使用して、関数呼び出しの内部に入ったり、関数呼び出しをスキップすることができる。

これにより、プログラムの動作を詳細に追跡することができる。

変数とレジスタの監視は、プログラムの実行中に変数やレジスタの値を確認する機能である。

ウォッチウィンドウに変数を追加することで、その値をリアルタイムで監視することができる。

これにより、プログラムの状態を把握し、期待通りに動作しているかを確認することができる。

MSP430G2553は16ビットRISCアーキテクチャを採用しており、16個の汎用レジスタ (R0~R15) を持つ。

メモリビューアは、マイコンのメモリ内容を直接確認する機能である。

フラッシュROM、SRAM、ペリフェラルレジスタ等のメモリ領域を表示して、必要に応じて値を変更することもできる。

これは、低レベルのデバッグや、ハードウェアの動作確認に特に有用である。

MSP430G2553のメモリマップは以下の通りである:

- フラッシュROM: 0xC000~0xFFFF (16[KB])

- 情報メモリ: 0x1000~0x10FF (256バイト)

- RAM: 0x0200~0x03FF (512バイト)

- ペリフェラル (16ビット): 0x0100~0x01FF

- ペリフェラル (8ビット): 0x0010~0x00FF

- 特殊機能レジスタ (SFR): 0x0000~0x000F

※注意

- デバッグ中は、マイコンの動作が通常とは異なる場合がある。

特に、タイマやウォッチドッグタイマの動作に影響が出る可能性がある。 - ブレークポイントで停止中は、ペリフェラルの動作も停止する場合がある。

これにより、実際の動作とは異なる結果が得られる可能性がある。 - MSP430G2553のハードウェアブレークポイント数は2個と限られているため、複雑なデバッグでは計画的に使用する必要がある。

ヒューズの設定とフラッシュ保護

MSP430マイコンには、セキュリティ機能としてフラッシュ保護機能が実装されている。

この機能を理解し、適切に使用することは、製品のセキュリティを確保する上で重要である。

フラッシュ保護の概念

フラッシュ保護は、マイコン内部のフラッシュROMに格納されているプログラムコードを、不正な読み出しや書き換えから保護するための機能である。

MSP430G2553では、JTAGセキュリティヒューズビットと呼ばれる特別なビットを設定することで、フラッシュ保護を有効にすることができる。

フラッシュ保護が有効になると、JTAGインターフェースを使用してフラッシュROMの内容を読み出すことができなくなる。

これにより、競合他社や悪意のある第3者がプログラムコードを盗むことを防ぐことができる。

保護の種類

MSP430G2553では、JTAGヒューズブロー機能により、以下の保護が提供される。

ヒューズが一度ブローされると:

- JTAG/Test機能へのアクセスが完全に無効化される

- Spy-Bi-Wire機能へのアクセスが完全に無効化される

- エミュレーション機能が無効化される

- JTAGは自動的にバイパスモードに切り替わる

- これにより、フラッシュROMおよび情報メモリの読み出しが不可能となる

情報メモリセグメントAには、デバイス固有のキャリブレーションデータが格納されている。

リセット後、セグメントAはプログラミングおよび消去から保護されている。

ロック解除は可能であるが、デバイス固有のキャリブレーションデータが必要な場合は、このセグメントを消去しないように注意する必要がある。

ヒューズブローの設定方法

JTAGセキュリティヒューズのブローは、開発環境のヒューズブロー機能を使用して実行する。

ヒューズブロー時の条件は以下の通りである:

- 供給電圧VCC: 2.5[V] (25℃時)

- TESTピンのヒューズブロー電圧VFB: 6[V]~7[V]

- ヒューズブロー中のTESTピンへの供給電流IFB: 最大100[mA]

- ヒューズブロー時間tFB: 最大1[ms]

Spy-Bi-Wire接続でヒューズブロー機能を使用する場合は、R2 (330[Ω]の保護抵抗) が必要である。

この抵抗は、JTAGデバッグインターフェースのTCK信号をヒューズブロー電圧から保護するためである。

※警告

ヒューズブローは完全に不可逆的な操作である。

一度ヒューズがブローされると、以下の状態となる:

- JTAGアクセスが永久に無効化される

- Spy-Bi-Wireアクセスが永久に無効化される

- フラッシュROMの内容を読み出すことができなくなる

- デバッグが完全に不可能となる

- 新しいプログラムの書き込みができなくなる

- デバイスの再プログラミングは不可能となる

したがって、ヒューズブローは、製品の最終出荷時にのみ実行することが強く推奨される。

開発やデバッグの段階では、絶対にヒューズブローを実行してはならない。

ヒューズブロー前の推奨手順

ヒューズブローを実行する前に、以下の手順を確実に実行すること:

- プログラムコードの完全なバックアップを複数の場所に保存する

- 製品の全機能テストを完了し、全ての機能が正常に動作することを確認する

- フラッシュROMの内容を読み出して、正しくプログラムされていることを確認する

- 製品が最終仕様を満たしていることを確認する

- ヒューズブローが本当に必要かどうかを再確認する

※注意

- ヒューズブローを実行する前に、必ずプログラムコードのバックアップを取ること。

- ヒューズブローを実行すると、デバッグが完全に不可能になる。製品の出荷前に十分なテストを行うこと。

- ヒューズブローは不可逆的な操作である。一度実行すると、JTAGアクセスを復元する方法は存在しない。

- 誤ってヒューズブローを実行した場合、そのデバイスは開発用途には使用できなくなる。

ブートローダー (BSL)

JTAGピンは、MSP430およびCC430デバイスのメモリへのアクセスを提供する。

一部のデバイスでは、これらのピンがデバイスのポートピンと共有されており、この共有が設計を複雑にしたり、共有自体が不可能な場合がある。

MSP430G2553では、P1.4~P1.7ピンがJTAG機能とGPIO機能で多重化されている。

BSLの概要

JTAGピンを使用する代わりに、MSP430G2553を含む多くのMSP430Fxxxデバイスには、より少ない信号線を使用してフラッシュメモリの消去とプログラミングを可能にするプログラム (ブートローダ、以前はbootstrap loaderとして知られている) が含まれている。

MSP430G2553のBSLは、UART (Universal Asynchronous Receiver/Transmitter) シリアルインターフェースを使用する。

BSLを使用したMSP430メモリへのアクセスは、ユーザー定義パスワードによって保護されている。

BSLの機能ピン

MSP430G2553の20ピンパッケージでは、BSL機能には以下のピンが使用される:

- データ送信: ピン3 (P1.1)

- データ受信: ピン7 (P1.5)

28ピンおよび32ピンパッケージでも同様のピン配置である。

BSLの利点

BSLを使用することで、以下に示すメリットが得られる。

- 必要な信号線が少ない (通常2本のUARTピン + 電源とGND)

- JTAGピン (P1.4~P1.7) を他の目的 (GPIO、タイマ出力、通信等) に使用できる

- 製品の最終基板でプログラミングが容易

- フィールドでのファームウェア更新が可能 (製品が市場に出た後でもソフトウェアを更新できる)

- JTAGヒューズをブローした後でも、BSLを使用したプログラミングは可能

設計上の推奨事項

Texas Instrumentsは、MSP430G2553を使用する開発者に対して、BSLを考慮した回路設計を推奨している。

具体的には、以下の信号へのアクセスを提供することが推奨される (例:ヘッダを使用):

- RST/NMIピン (ピン16)

- TEST/SBWTCKピン (ピン17)

- BSL通信に必要なUARTピン (P1.1とP1.5)

これにより、開発段階ではJTAG/Spy-Bi-Wireを使用し、製品化後はBSLを使用してファームウェア更新を行うという柔軟な設計が可能となる。

BSLの詳細情報

BSLの機能と実装の詳細については、「MSP430 Programming Via the Bootstrap Loader User's Guide (SLAU319)」を参照すること。

また、TI社のMSP430ウェブサイトでは、アプリケーションレポートとMSP430 BSLツール開発者のリストが提供されている。

※注意

BSL機能を使用する場合は、セキュリティパスワードを適切に管理すること。

パスワードが漏洩した場合、不正なファームウェア更新が可能となる恐れがある。

製品のセキュリティ要件に応じて、BSLのパスワード保護を適切に設定すること。

LaunchPad開発キット (MSP-EXP430G2ET)

MSP430G2553には、専用の開発キットであるMSP-EXP430G2ET LaunchPad Development Kitが用意されている。

このキットは、MSP430G2553の開発を容易にするために設計された低コストの開発プラットフォームである。

eZ-FETオンボードデバッグプローブ

MSP-EXP430G2ETには、eZ-FETと呼ばれるオンボードデバッグプローブが搭載されている。

これにより、高価な外部プログラマを購入する必要なく、すぐに開発を開始できる。

eZ-FETは、全てのMSP430マイコンをサポートするシンプルで低コストなデバッガである。

USB経由でPCに接続され、Spy-Bi-Wire (SBW) インターフェースを使用してターゲットMSP430G2553と通信する。

また、eZ-FETはEnergyTrace™技術をサポートしており、アプリケーションの消費電力をリアルタイムで測定・表示することができる。

これにより、省電力設計の最適化が容易になる。

アイソレーションジャンパブロック

MSP-EXP430G2ETには、eZ-FETとターゲットMSP430G2553の間にアイソレーションジャンパブロックが配置されている。

このジャンパブロックにより、以下の機能が提供される:

- eZ-FETとターゲットドメイン間の3.3[V]および5[V]電源フローを制御

- オンボードデバッグおよびアプリケーションUART通信以外の用途でターゲットMCUピンを露出

- eZ-FETのプログラミングおよびUARTインターフェースを露出し、オンボードMCU以外のMCUに使用可能

ジャンパブロック接続:

- GND: グラウンド

- 5V: USBからの5[V] VBUS

- 3V3: eZ-FETドメインでVBUSから生成された3.3[V]レール

- RXD <<: バックチャネルUART (ターゲットG2553がこの信号を介してデータを受信)

- TXD >>: バックチャネルUART (ターゲットG2553がこの信号を介してデータを送信)

- SBW RST: Spy-Bi-Wireデバッグ - SBWTDIOデータ信号 (RST信号としても機能、アクティブLow)

- SBW TST: Spy-Bi-Wireデバッグ - SBWTCKクロック信号 (TST信号としても機能)

バックチャネルUART

バックチャネルUARTは、ターゲットアプリケーションの主要機能の一部ではないUSBホストとの通信を可能にする。

これは、開発中に有用であり、PCホストへの通信チャネルも提供する。

この通信を使用して、PCでグラフィカルユーザーインターフェース (GUI) やその他のプログラムを作成し、LaunchPad開発キットと通信することができる。

バックチャネルUARTは、USCI_A0上のUARTである (MSP430G2553のP1.1とP1.2を使用)。

BoosterPackプラグインモジュール対応

LaunchPad開発キットは、20ピンLaunchPad開発キットピンアウト標準に準拠している。

この標準は、TIエコシステム全体でLaunchPad開発キットとBoosterPackプラグインモジュールツール間の互換性を支援するために作成された。

MSP-EXP430G2ET LaunchPad開発キットは、標準に準拠した全ての20ピンBoosterPackプラグインモジュールと互換性がある。

BoosterPackプラグインモジュールがMSP-EXP430G2ET LaunchPad開発キットとの互換性を明示的に示していない場合は、

候補となるBoosterPackプラグインモジュールの回路図とLaunchPad開発キットを比較して、互換性を確認すること。

BoosterPack Checkerツールを使用して、選択したLaunchPad開発キットと任意の数のBoosterPackプラグインモジュールの互換性を確認することができる。

外部ターゲットへの接続

eZ-FETは、オンボードのMSP430G2553だけでなく、外部のターゲット基板をプログラミングおよびデバッグするためにも使用できる。

外部ターゲットに接続するには:

- アイソレーションジャンパブロック内の全てのジャンパを取り外す (デバッグプローブは一度に複数のターゲットにSpy-Bi-Wire接続できないため)

- ターゲット基板がSBWに適合する適切な接続を持っていることを確認する (RST/SBWTDIOのコンデンサは2.2[nF]以下でなければならない)

- アイソレーションジャンパブロックのデバッグプローブ側からターゲットハードウェアに以下の信号を接続:

- 5V (5[V]が必要な場合)

- 3.3V

- GND

- SBWTDIO

- SBWTCK

- TXD (UARTバックチャネルを使用する場合)

- RXD (UARTバックチャネルを使用する場合)

この配線は、ジャンパワイヤを使用するか、アイソレーションジャンパブロックに差し込むコネクタを備えた基板を設計することで行うことができる。

※注意

LaunchPad開発キットを使用する場合は、必ずMSP-EXP430G2ETのユーザーガイドを参照すること。

ハードウェア設計ファイル、ソフトウェアサンプル、詳細な仕様は、TI社のウェブサイトからダウンロードできる。

トラブルシューティング

ターゲットデバイスが認識されない

この問題は、MSP-FETとターゲットマイコン間の通信が確立できない場合に発生する。

まず、ターゲット基板に電源が供給されていることを確認する。

MSP-FETは、ターゲット基板の電源電圧を検出するため、電源が供給されていない場合、通信は確立できない。

テスターを使用して、DVCCピン (20ピンパッケージではピン1) に正しい電圧 (1.8[V]~3.6[V]) が供給されているかを確認する。

次に、JTAGケーブル または Spy-Bi-Wireケーブルの接続を確認する。

ケーブルが正しく接続されているか、ピンの向きが正しいかを確認する。

ケーブルが緩んでいたり、接触不良がある場合、通信エラーが発生する可能性がある。

また、RSTピンとTESTピンの状態を確認する。

これらのピンが他の回路によって固定されている場合、JTAGモードに入ることができない可能性がある。

RSTピンには外部プルアップ抵抗 (47[kΩ]) が、TESTピンには内部プルダウン抵抗 (典型値60[kΩ]) が接続されていることを確認する。

さらに、ターゲットマイコンのJTAGピン (P1.4~P1.7) が他の目的で使用されていないかを確認する。

プログラムコードでこれらのピンをGPIOとして設定している場合、JTAG通信が妨げられる可能性がある。

この場合、フラッシュ消去モードでマイコンに接続し、フラッシュROMを消去してから再度プログラムをダウンロードする必要がある。

電源供給方法(VCC_TOOLとVCC_TARGET)の選択が正しいかも確認する。

両方に接続されている場合や、いずれにも接続されていない場合は、正しく動作しない。

RST/NMI/SBWTDIOピンのコンデンサC1の容量を確認する。

C1が2200[pF]を超えている場合、Spy-Bi-Wire通信が正常に動作しない可能性がある。

推奨値は1100[pF]、許容範囲は100[pF]~2200[pF]である。

プログラムのダウンロードに失敗する

プログラムのダウンロード中にエラーが発生する場合、いくつかの原因が考えられる。

まず、ターゲット基板の電源電圧が安定していることを確認する。

電源電圧が不安定な場合、書き込み処理中にエラーが発生する可能性がある。

オシロスコープを使用して、電源電圧の変動を確認することができる。

デカップリングコンデンサ (C3 = 0.1[µF]) が適切に配置されているかも確認する。

特に重要なのは、フラッシュROMのプログラミングまたは消去時には、電源電圧が2.2[V]~3.6[V]の範囲内であることである。

電源電圧が2.2[V]未満の場合、フラッシュROMへの書き込みは失敗する。

次に、フラッシュROMの容量を確認する。

プログラムサイズが、MSP430G2553のフラッシュROM容量 (16[KB]) を超えている場合、書き込みは失敗する。

コンパイル後のプログラムサイズを確認し、必要に応じてコードを最適化する。

また、JTAGセキュリティヒューズがブローされていないかを確認する。

ヒューズがブローされている場合、新しいプログラムを書き込むことができない。

ヒューズのブロー状態は不可逆的であり、一度ブローされたデバイスは再プログラミングできない。

デバッグ中に通信が切断される

デバッグ中に通信が切断される場合、以下の点を確認する。

まず、USBケーブルの接続を確認する。

USBケーブルが緩んでいたり、接触不良がある場合、通信が切断される可能性がある。

別のUSBポートやUSBケーブルを試してみることも有効である。

次に、JTAGケーブル または Spy-Bi-Wireケーブルの長さを確認する。

ケーブルが長すぎる場合、ノイズの影響を受けやすく、通信エラーが発生する可能性がある。

ケーブルの長さを0.2[m]以下にすることが推奨される。

また、ターゲット基板の周辺にノイズ源がないかを確認する。

モーターやスイッチング電源などのノイズ源は、JTAG/Spy-Bi-Wire通信に影響を与える可能性がある。

可能であれば、ノイズ源から離れた場所でデバッグを行う。

さらに、プログラムコードでウォッチドッグタイマを使用している場合、デバッグ中にウォッチドッグタイマがマイコンをリセットする可能性がある。

デバッグ時には、ウォッチドッグタイマを無効にするか、適切に制御する必要がある。

MSP430G2553では、WDTCTLレジスタを使用してウォッチドッグタイマを制御する。

SBW (Spy-Bi-Wire) 通信使用時の特有の問題として、TEST/SBWTCKピンの意図しないエッジによる通信切断がある。

TEST/SBWTCKピンが立ち上がりエッジに敏感なため、ノイズや不適切な配線により通信が切断される可能性がある。

この場合、500[Ω]~1[kΩ]のプルダウン抵抗を追加することを検討する。

ファームウェアの更新が必要な場合

MSP-FET自体のファームウェアが古い場合、新しいマイコンデバイスをサポートしていない可能性がある。

ファームウェアの更新は、Code Composer Studioなどの開発環境から行うことができる。

通常、開発環境がMSP-FETのファームウェアを自動的に検出し、必要に応じて更新を促す。

ファームウェアの更新プロセスは、通常数分で完了する。

更新中は、MSP-FETをコンピュータから取り外さないように注意する必要がある。

MSP430G2553を使用する場合は、比較的新しいファームウェアバージョンが必要である。

古いMSP-FETファームウェアでは、MSP430G2553を正しく認識できない場合がある。

MSP-EXP430G2ET LaunchPadの問題

MSP-EXP430G2ET LaunchPad開発キットを使用している場合、以下に示す事柄も確認する。

- アイソレーションジャンパブロックのジャンパが全て正しく接続されているかを確認する。

- 外部ターゲットに接続する場合は、全てのジャンパを取り外す必要がある。

- eZ-FETのファームウェアが最新であることを確認する。

※注意

- MSP-EXP430G2ET LaunchPadに関する情報は、MSP430G2553 LaunchPad Development Kit (MSP-EXP430G2ET) User's Guide (SLAU772) を参照すること。